# **EURO-MILS**

Secure European Virtualisation for **Trustworthy Applications in Critical Domains**

# **MILS Architecture**

318353

**Project number**

**Project acronym EURO-MILS**

**Project title EURO-MILS**:

> Secure European Virtualisation for Trustworthy Applications Critical

Domains

1<sup>st</sup> October, 2012 Start date of the project

**Duration** 36 months

**Programme** FP7/2007-2013

**Project website** www.euromils.eu

**Editors/Authors:** Holger Blasum (SYSGO AG), Sergey Tverdyshev, Bruno Langenstein (DFKI / Deutsches Forschungszentrum für künstliche Intelligenz), Jonas Maebe, Bjorn De Sutter (Universiteit Gent), Bertrand Leconte, Benoît Triquet (AIRBUS), Kevin Müller, Michael Paulitsch (EADS Deutschland GmbH), Axel Söding-Freiherr von Blomberg (OpenSynergy GmbH), Axel Tillequin (EADS France SAS)

Further information on the EURO-MILS Project: http://www.euromils.eu

The research leading to these results has received funding from the European Union's Seventh Framework Programme (FP7/2007-2013) under grant agreement number 318353.

# Whitepaper 2014

## **Executive Summary**

We introduce a generic description of MILS systems (Chapter 2), and the MILS architecture template (Chapter 3). Chapter 4 discusses MILS main components. The practical aim of this document is two-fold: (1) to get a common understanding of MILS terms and definitions, and (2) to provide a framework to derive the information flow, access control and resource allocation of the demonstrators from individual MILS components.

## **Table of Content**

| Chap | ter 1   | Introduction                             | 1    |

|------|---------|------------------------------------------|------|

| Chap | ter 2   | MILS concepts and state of the art       | 2    |

| 2.1  | Modu    | lar high-assurance safety in avionics    | 2    |

| 2.2  | Modu    | lar high-assurance computer security     | 3    |

| 2.3  | Certifi | ication aspects                          | 7    |

| 2.4  | Archit  | ectural decomposition and modelling      | 8    |

| Chap | ter 3   | MILS representation adopted by EURO-MILS | . 10 |

| 3.1  | MILS    | architecture template                    | . 10 |

| 3.2  | MILS    | terminology                              | . 16 |

| 3.3  | Exam    | ple of a MILS system                     | . 22 |

| Chap | ter 4   | MILS main components                     | . 24 |

| 4.1  | Softw   | are components                           | . 24 |

| 4.2  | Hardv   | vare components                          | . 37 |

| 4.3  | Syste   | m configuration of components            | . 42 |

| Chap | ter 5   | Conclusion                               | . 45 |

| 5.1  | Overv   | riew of component policies and reuse     | . 45 |

| 5.2  | Secur   | e design principles                      | . 47 |

| 5.3  | Resul   | ts                                       | . 48 |

| 5.4  | Ackno   | owledgment                               | . 49 |

| Chap | ter 6   | Glossary                                 | . 50 |

| Chap | ter 7   | List of Abbreviations                    | . 54 |

| Chap | ter 8   | Bibliography                             | . 56 |

## **Chapter 1** Introduction

EURO-MILS claims that "the project's cornerstone is MILS (Multiple Independent Levels of Security), a high-assurance security architecture that supports the coexistence of untrusted and trusted components, based on verifiable separation mechanisms and controlled information flow" [Cordis12]. While MILS is well established in practice, and products claiming MILS compliance do exist since the mid 2000s, it so far has not been standardized or given a formal definition, in particular "there is no standard that defines which functionalities reside in a MILS-compliant system and how a MILS kernel should be designed." [DPF09, p. 4].

In the absence of such a standard, to reflect meaningfully MILS, a common understanding of some terms related to "architecture" is helpful. We introduce a generic description of MILS systems (Chapter 2), and the MILS architecture template (Chapter 3). Chapter 4 discusses MILS main components.

December 2014 Page 1 of 63

## **Chapter 2** MILS concepts and state of the art

In publications on MILS such as [AFHOT06] reference is made to high-assurance safety (in particular avionics) and high-assurance security. We briefly recapitulate both backgrounds, based on well available material, without claiming to completely cover each development until the present. We also introduce certification and architectural decomposition and modelling aspects of MILS.

#### 2.1 Modular high-assurance safety in avionics

Safety assurance levels: [ARP4754] introduces a notion of safety assurance levels: if the failure of an application would have an impact that causes severe damage (e.g. loss of aircraft), the application is of a high assurance level. Otherwise, if the failure of an application would have an impact that causes a minor nuisance (e.g. loss of passenger entertainment system), the application is of a low assurance level. Applications at a high safety assurance level have stronger process requirements (planning, development, verification) than applications at a low safety assurance.

*IMA:* Integrated Modular Avionics (IMA) is an architectural concept for modular avionics software systems that has been inspired from previous architectural concepts for physically modular hardware systems that consisted of LRUs (Line Replacement Units). IMA replaces multiple instances of separate and dissimilar LRUs with fewer common processing modules, and provides shared power supplies, housing and communication links. IMA decomposes an IMA *system* into (1) an IMA *platform* consisting of hardware and core software doing resource management and process scheduling, and (2) IMA *applications*, which are software components interacting with the IMA platform.

IMA systems are designed to host several applications with appropriate isolation on a set of shared hardware and software resources. In IMA, applications execute in an environment generally called a set of partitions. A *partition* is a unit of separation regarding resource (i.e., CPU, memory, etc.) allocation in space and time domains. The IMA architecture dictates the underlying operating system (OS) to be developed for hard real-time, safety critical avionics applications. One of the functional requirements applied to such an OS is to host multiple independent aircraft applications while the computing platform shall not introduce significant common failure modes between those applications; evidences of the mechanisms providing isolation between those applications shall be demonstrated. One upside is that this enables incremental qualification, under which one application can be upgraded without requiring the others to undergo new certification.

IMA-related standards include a common interface for applications [ARINC653], and guidance for the development and certification of systems [DO-297].

[ARINC653] requires an operating system to manage partitions and a rich set of interfaces to manage their inter-partition communication, periodic assignment of CPU

December 2014 Page 2 of 63

time to a partition, applications ("processes") within a partition, memory allocation, and a health monitor responsible for reporting hardware, operating system software and application failures. [ARINC653] provides implementable interfaces for the above-mentioned functionalities (e.g., parameters and return values including error codes are defined).

Processes for the system development, certification planning, requirements determination, safety assessment, implementation verification and process assurance have been developed for complex integrated systems in avionics in general [ARP4754]. Similarly, [DO-297] describes the IMA-specific aspects of design assurance for all parties involved in development, integration, verification and validation of IMA systems. As considerations of the IMA platform, [DO-297, p. 11] availability (functional performance and resource management, health monitoring), integrity (including protection features, fault detection and partitioning), safety (appropriate architecture and design assurance), fault management and composability. [DO-297, p. 14] defines the aim of "robust partitioning" to provide an equivalent level of functional isolation and independence as a federated system implementation. A partitioning analysis demonstrates that "no application or subfunction in a partition could affect the behaviour of a sub-function or application in another partition in an adverse manner". [DO-297] splits validation, verification, configuration management and certification processes into tasks done at the application level, the platform level, and the system level.

IMA design is made to provide high-assurance safety systems for avionic industry. However, IMA requirements and development do not include security aspects, only random hardware faults and involuntary design errors are considered without taking into account failures due to malicious actions.

## 2.2 Modular high-assurance computer security

Security assurance levels: In computer security, the Common Criteria for Information Technology Security (CC, [CC12]) standard states that owners of assets (something valuable, e.g. a component in an aircraft or important data) place value on the assets. The risk of a threat to an asset "depends on the likelihood of the threat being realised and the impact on the assets when that threat is realised" [CC12, Part 1, p. 39]. Similar to the concept of safety assurance levels, an application which, under attack, impairs assets of high value (e.g., confidentiality of top secret data, integrity of a critical system) needs to provide a high security assurance and an application which, under attack, impairs assets only of low value needs to provide a low security assurance. Security assurance levels for individual components are especially used for standards that typically analyze distributed systems such as [ARINC811] for avionics and [ISA62443] for industrial automation.

Evaluation assurance levels: However, there is an additional difference in computer security versus safety: safety assurance usually considers probabilities of faults (e.g., ARP 4761, ISO-26262), and in systems, combined and dependent probabilities (e.g. "fault tree analysis"). In computer security, security risks are more "all or nothing": for example, once an attacker knows that access to an asset is possible by exploiting two weaknesses successively, he/she will perform those actions in the required

December 2014 Page 3 of 63

order. In particular this also holds if a larger system is incorrectly *specified*, and exploits against the larger system can be derived simply by analysis of the specification. In [CC12, Part 1, p. 41] the sufficiency of the countermeasures against a threat is thus shown by analysis in a document (the "Security Target"), and the correctness of a product is shown by evaluation in a graded evaluation process. If a product has undergone an extensive evaluation process, it gets assigned a high evaluation assurance level (EAL). If a product only has undergone a more limited evaluation process, it gets assigned a low evaluation assurance level.

Security policy and security policy levels: To build systems on consistent specifications, a security policy is imposed upon a system. A security policy often assigns security policy levels to elements of a system. A widely applied security policy for confidentiality was Bell-LaPadula that assigned to each component a label indicating a security level such as "public", "classified", "secret", "top secret", where "public" is less than "classified", "classified" less than "secret" and "secret" less than "top secret". On such a policy, each pair of components can be compared (a set with such features is also called a "total order"). It allows implementing schemes such as Bell-LaPadula, which (in simple terms) says that no-one is allowed to "read up" (read information of a higher security level than his/her classification) or to "write down" (write information to a lower security level than his/her classification). Bell-LaPadula was also chosen as the reference model for the Orange Book [Dod83]. Similarly, the Biba integrity policy can be seen as inverting the labels ("no write up", "no read down").

Multi-level secure systems (MLS): An MLS system maintains multiple security policy levels at the same time, often by assigning security labels to its components and resources. Systems implementing the afore-mentioned Bell-LaPadula or Biba models have been called MLS systems [And08]. A broader definition of the term MLS will be discussed under "MLS versus MILS nowadays" below.

Operating systems: Much early work in high-assurance modular computer security has been on secure operating systems [MP97]. The earliest uses of computers involved programs directly operating on hardware, addressing individual memory cells directly and exclusively using the entire hardware. However, maintainability concerns lead to the development of a more modular usage, by installing an operating system on the hardware. An operating system is a software system that (1) simplifies access to underlying hardware by providing appropriate abstractions to applications, (2) provides resource management (e.g. memory) and in particular is able to allocate CPU(s) to applications (scheduling). Operating systems also can provide networking or file system infrastructure to computers.

Security kernels: Many secure operating systems have used security kernels [MP97]. Security kernels have a small implementation, and thus can be more easily reviewed than a complex operating system. Security kernels target integrity, availability, and (usually a lesser concern in safety) confidentiality of applications and data and impose a security policy on the system. Security kernels, for example Honeywell's Scomp [Fr83], supporting a security policy with multiple security policy levels had usually been subsumed under "multi-level secure" (MLS) systems.

December 2014 Page 4 of 63

In a security kernel, applications that are running at a certain security policy level fixed for each application are called "single-level secure" (SLS). If multiple instance of one SLS implementation are deployed in a system while each of those instances processes a different security level it will lead to "multiple single-level secure" (MSLS) components. Applications may implement security policies on completely different features than security kernels, so policies provided by applications versus policies provided by the separation kernel cannot always be directly compared. However, an implicit requirement on security kernels is that their security assurance level is at least as high as or higher than the highest security assurance level found in any application.

Classification of applications in a security kernel: Unless otherwise specified, the applications are SLS. Applications spanning multiple security policies are also MLS, such as a downgrader. For a collection of classifications, see Table 1. The underlying idea of such classification is that, from an information flow policy and resource sharing viewpoint only MSLS and MLS components need to be verified [AFHOT06].

| SLS: Single-Level<br>Secure Components<br>[Alv98, AFHOT06,<br>ZAV06]   | A Single Level Secure Component is a component that every time processes data of one security level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSLS: Multiple<br>Single-Level Secure<br>Component<br>[AFHOT06, ZAV06] | A Multiple Single-Level Secure Component is a special kind of SLS component that processes data of multiple security levels, but always maintains separations between classes of data by exclusively processing only one security level during its runtime instance. For example this separation can be implemented by allowing access to a different security level only when the component has rebooted with different parameters. Also deploying multiple instances of one SLS component processing different single security levels turn this SLS component into an MSLS component. |

|                                                                        | Note: in [Alv98] this was restricted to temporal separation, "at a single time-point, only handles information from one component". If such a single-level process is to be implemented as untrusted process [Alv98], it can be supplemented by an appropriate labelling and filtering of messages. Moreover, in [Alv98] SLS and MSLS are subsumed under "secure single-level process".                                                                                                                                                                                                 |

| MLS: Multi-Level<br>Secure Component<br>[Alv98, AFHOT06,<br>ZAV06]     | A Multi-Level Secure Component is a component that handles information of with different security levels concurrently during one runtime instance. An example of an MLS component is a separation kernel [MPT+12] or a downgrader [ZAV06].                                                                                                                                                                                                                                                                                                                                              |

| ,                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 1: Levels of components

December 2014 Page 5 of 63

Multiple independent levels of security (MILS): Encoding rich functionality into a central component raises the question of how to design a security kernel that is itself secure. Therefore, the functionality of security kernels has been broken up into a more structured design. To differentiate such systems from "MLS" systems, the term "MILS" (multiple independent levels of security) has been introduced. It describes systems where different partitions hosting applications are either independent from each other or connected by communication channels without an explicit hierarchical ordering policy that would require attaching global security policy levels to each partition.

The MILS architecture approach was popularized by John Rushby in 1981 ([Rus81], "Design and Verification of Secure Systems"; at that time, Rushby did not use the term MILS), which started a formalisation of MILS concepts. In his approach, the system is designed as a distributed one and is based on a special kind of operating system using a separation kernel (SK). He proposed that the security should be achieved partly through physical separation, partly through the use of components and partly through trusted functionalities performed within some components. The purpose of the separation kernel is to allow such a "distributed" system to run within a single processor. This is achieved by offering a very strong separation between the different partitions except for very carefully controlled information flow between them.

The basic idea of MILS is to make the security-critical part of the system (i.e., SK) small enough and with specific functionality so it can be certified at high assurance levels. Traditional operating system services like device drivers, file system, etc. are pulled out of the separation kernel and run in non-privileged mode; the only part of the MILS system running in privileged mode is the SK. Safety and security policies must be enforced at each level: by the separation kernel and by any other component needed by the applications hosted in the partitions, but also by the applications themselves. A key MILS objective is to enable the evaluation and certification of a complex system to be modularized into a number of independent, small evaluations.

*MILS* separation kernel security assurance characteristics: In practice, MILS principles largely match the requirements imposed by users and producers of IMA systems who, in addition to their IMA safety requirements, had an additional need for security requirements.

In the MILS literature, explicit concerns for security assurance have been formulated as "NEAT" [BBH+05, KW08, UV05], as follows:

- **Non-bypassable:** Policy enforcement functions cannot be circumvented.

- **Evaluatable:** Policy enforcement functions are small enough and simple enough that proof of correctness is practical and affordable.

- Always Invoked: Policy enforcement functions are invoked each and every time.

- **Tamperproof:** Policy enforcement functions and the data that configures them cannot be modified without authorization.

Similar definitions exist elsewhere, e.g. "evaluatable", "always invoked", "tamperproof" for reference monitors in [And72, p. 22].

December 2014 Page 6 of 63

Objectives and threats in MILS systems: In computer security, a threat is characterized by some adverse action achieved by an attacker who attacks system assets. The objectives of computer security are to counter threats in order to mitigate the risk of a threat scenario.

Assets for MILS system and its components can be formulated in a straightforward way:

- for each component itself,

- with the objectives of the preservation of its confidentiality, integrity, and (possibly) availability,

- for each resource the component uses,

- with the objectives of the preservation of its confidentiality, integrity, and (possibly) availability.

Threats can be named against the preservation of each the security attributes:

- for confidentiality, the threat is disclosure,

- for integrity, the threat is modification,

- for availability, the threat is depletion.

MLS versus MILS nowadays: Earlier in this section ("Multi-level secure systems (MLS)") a strict hierarchically ordered security policy based on security policy levels had been discussed in the context of MLS. One insight gained by the MILS approach was that several components on the same platform have safety and security requirements that are just "different" in a wider sense. This insight had led to (1) applying the term MLS also in that wider sense [DCS+04, LRP+11], and (2) to use MILS to describe an architectural decomposition approach of an MLS system into components [Alv98, AFHOT06, ZAF08]. For the rest of this document we use the term MLS for systems based in the wider sense (1) and MILS for the architectural decomposition approach (2).

## 2.3 Certification aspects

For IMA, DO-297 describes how to perform incremental certification [DO-297, WP08]. A case study on compositional certification of a system built on a separation kernel using Common Criteria approach is given in [MPS+12].

The Open Group plans to develop a catalogue of components under the "Mils<sup>(TM)</sup>" (this spelling) trademark that are backed by an Open Group Mils protection profile. [RD07, Del10] list protection profiles for MILS components such as console system, a network system and a file system, and suggest to specify the allocation of trust of specific MILS components to a MILS Integration Protection Profile (MIPP); however, these PPs are in draft form and are not public.

[SKPP] was a protection profile for separation kernels running on hardware. Successful certification was achieved for the Green Hills Integrity system running on PowerPC 750CXe PCI extension card [Gre08]. However, [SKPP] has been retracted ("sunsetted") by NSA in September 2011. The published rationale for the sunsetting includes the considerations (1) that the NSA "will focus on specific government"

December 2014 Page 7 of 63

systems using separation kernels rather than general OS evaluation" [Wis11], and points [Hou11] to that (2) in the project "one box one wire" (OB1) "the underlying commodity workstation (as part of a separation platform) does not appear to be appropriate for SKPP certification due to its complexity" and that "the problem with commodity desktop platforms comes down to the fact that too many developers and vendors are interdependent" [SNAC10]. In balance, in the same document, it is pointed out that "commodity workstations may present a completely acceptable risk profile given available options" and the "findings in this document do not condemn OB1 or the use of separation kernels in commodity workstations", [SNAC10, also discussed in NG12]. Note: concerning (1), this policy change does not apply to Europe, concerning (2), our certification approach for the separation kernel component does not include the hardware. That is, we assume that either the hardware has been certified by the CC, or it is trusted to be reliable for other reasons, e.g. by evidence from the hardware vendor that the hardware is suitable for the security-critical purpose intended.

For partitioning communications systems (PCS), a protection profile draft exists [Uch05] (available on demand from the author) which extends the PIFP (partitioned information flow policy) from [SKPP] to distributed environments. The High Assurance Security Kernel protection profile [HASK] also addresses distributed communication systems in the style of a PCS.

#### 2.4 Architectural decomposition and modelling

Since a long time research on security software architecture has emphasized principles that also can be found in MILS systems. For example, discussing mechanisms and techniques that define who may use or modify the information stored in a computer, Saltzer and Schroeder have pointed out that the design shall be kept "as simple and small as possible" [SS75, p. 1282], that "every access to every object" shall be checked and that the design shall be open (not secret). As they are widely known, we will revisit the [SS75] design principles and the extent to which they are fulfilled later (in Section 5.2).

In the context of *general* research on software architecture, the MILS approach with its strong emphasis on how a system is composed would subsumed under a structural model which is characterized by components, connectors and additional constraints [BCK03, SG95, ZAF06, ZAF08]. A MILS channel is a "connector" and the additional constraint on the system ("other stuff" in [SG95]) is non-interference. For component-connector type systems, [CBB+03, Section 4.7] proposes documentation in the form of either Architecture Description Languages or UML. If UML is used, [CBB+03, Section 4.7] discusses how to represent components and connectors in UML and note that connectors can be either expressed as dependencies between a component, and the ports/interfaces realized by the component or as components themselves (p. 162). [ZAF06, ZAF08] discuss decomposition patterns for components such as "product pattern", "cascade pattern", "feedback pattern" and several instances of "aggregation patterns".

The secure refinement of a downgrader with regards to information flow properties is demonstrated by a paper-and-pencil argument in [CVdM09].

December 2014 Page 8 of 63

MILS architectures have been expressed in Architecture Analysis and Design Language (AADL), verified by the REAL tool [GH08], and then been used for code generation by [DPK10]. MILS components have been expressed in the LOTOS language by [Alv98]. In [BBH+05], boundary flow modelling and secure UML are listed as possible support to the system integrator. The software engineering tool Specware for the breakup of a system has been used by [MWTG00]. [Cof11] discusses identification of architecture design patterns on an IMA system.

December 2014 Page 9 of 63

# Chapter 3 MILS representation adopted by EURO-MILS

This chapter presents the EURO-MILS project view of a MILS architecture template using a top-down approach (Section 3.1), followed by a bottom-up approach giving definitions of terms considered useful to describe the MILS architecture template (Section 3.2). We conclude this chapter with an example (Section 3.3).

#### 3.1 MILS architecture template

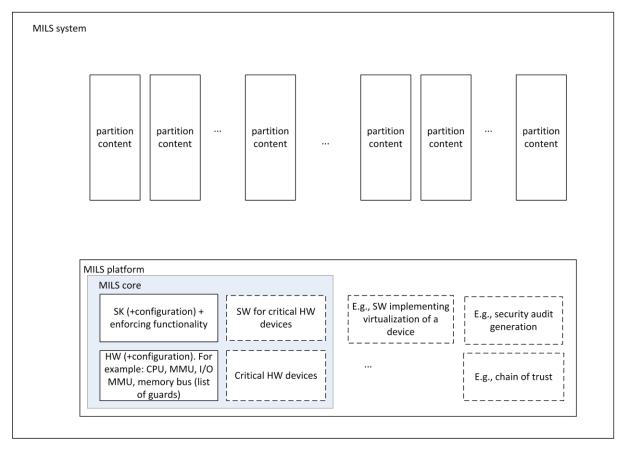

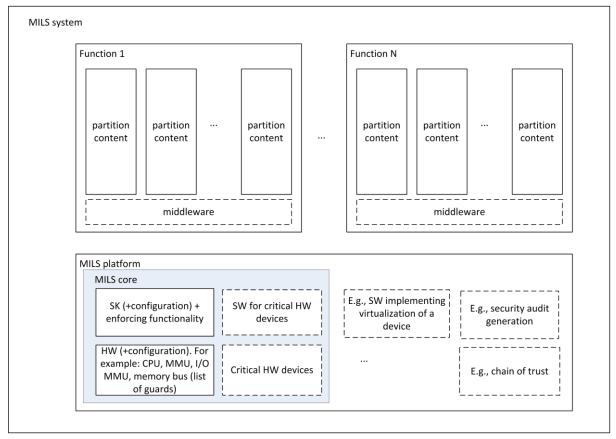

Figure 1 presents a high-level view of a MILS architecture template. This is the template we adopt in the EURO-MILS project. The term "MILS architecture template" names a template encompassing many possible MILS systems, whereas the term "MILS architecture" (without "template") refers to the architecture of the implementation of a concrete MILS system.

From the outside (i.e., external world, which could be a larger system comprising the MILS system), the MILS system is seen as a system that handles information from multiple components with different security and safety levels concurrently, in other words, an MLS system. The MILS system's internal architecture is not visible from the point of view of the infrastructure around the MILS system (it is like a black box). Thus, a MILS system can be used as a base to build a system that has different safety/security requirements for different components, called an MLS system.

In the rest of the section, we are discussing in more details each part shown in Figure 1.

December 2014 Page 10 of 63

Figure 1: MILS architecture template (components in dashed lines are optional).

#### 3.1.1 MILS system

We define a MILS system as a system where its MILS architecture is visible to the person composing the MILS system from its components, i.e., the *system integrator*.

A MILS system consists of components interacting with each other. We define three main components in a MILS system:

- MILS core (Section 3.1.2)

- MILS platform (Section 3.1.3)

- Partition (Section 3.1.4)

December 2014 Page 11 of 63

#### 3.1.2 MILS core

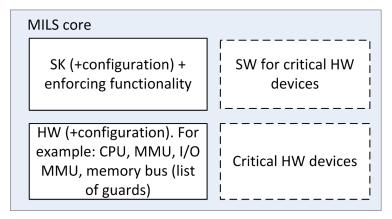

Figure 2: MILS architecture template: MILS core

The only goal of the MILS core is to provide separated partitions with controlled information flow between them. Thus, the MILS core provides the primary security functionality of a MILS system. The MILS core (Figure 2) consists of components that implement and enforce the separation both in space and time: separation-supporting hardware and the separation kernel. Depending on use-case implementation, the MILS core may also include hardware critical devices and software for these hardware devices.

Separation-supporting hardware.

This hardware consists of implementation (gates in silicon) and configuration/initialization.

The hardware shall support separation, e.g. CPU with different privilege modes, MMU, memory bus, IOMMU. Hardware consists of interconnected components. A hardware component's interactions with other hardware components can be restrained by a guard. For example

- Let's consider a CPU, memory, and MMU. Assume the CPU is working in a user mode. In this mode, the CPU can only access memory if the access has been permitted by the MMU. Thus, the MMU is the guard for the CPU.

- Let's consider a device, memory, and IOMMU. Assume the device accesses memory as a DMA. In this case, DMA access will happen only if the IOMMU permits it. Thus, the IOMMU is the guard for this device.

Configuration/initialization is software that performs hardware-specific initialization and configuration of hardware, e.g. firmware and/or bootloader and/or standalone software.

Separation kernel.

The separation kernel guarantees separation and controlled information flow by enforcing the security policy.

Examples of enforced security polices are

resource allocation policy (e.g. allocation of CPU time and memory to partitions),

December 2014 Page 12 of 63

- access control policy (e.g. access rights to objects under control of separation kernels),

- o information flow policy (e.g. communication rights of partitions).

Separation kernel functionality relies on the hardware supporting functionality.

A separation kernel may further configure hardware with the respect to a given security policy. For example, it configures guards, creates page tables and sets MMUs.

Critical hardware parts/devices.

These devices can bypass the enforcement mechanisms of the separation kernel. For example, DMA capable devices without guards (i.e. without IOMMU) can bypass the separation kernel. To have such critical devices is optional. However, if such device is present, its associated software acting as a guard for it must be also present in the architecture.

Software for critical hardware parts/devices.

This software is the guard for a critical device. It provides an API to partitions to work with the device. Therefore, this software implements and enforces part of the separation. We assume that if the software correctly works with the device, the device will not bypass the separation kernel security policies.

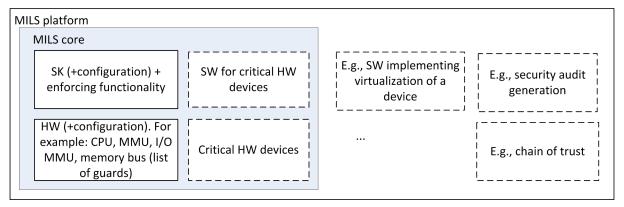

#### 3.1.3 MILS platform

Figure 3: MILS architecture template: MILS platform

The MILS platform (Figure 3) consists of the MILS core and optional software and/or hardware components that provide secondary security functionalities and do not contribute to the enforcing of separation. These are security services that can be used based on the use-case needs.

These optional components are part of the platform because they

- contribute to the system security, however, they do not enforce separation between partitions,

- · can be used by several partitions,

- may be realized by different implementations for a given optional security service (use-case dependent),

December 2014 Page 13 of 63

might need a tighter integration with separation kernel or hardware.

Examples of such optional components are:

- security audit (Section 3.1.5),

- o crypto functionality shared between partitions,

- o software implementing virtualization of devices (e.g., multiplexing of accesses for the network interface, shared graphics or shared audio).

#### 3.1.4 Partition

A partition is a unit of the separation created by the MILS core. A partition will get resources as specified in a security policy and enforced by the MILS core. A partition is a container that hosts executable and/or non-executable data. An executable in the partition can use allocated resources, communicate with the MILS core, and communicate with other partitions under control of the MILS core if such communication is explicitly allowed by the security policy.

Partitions also may include hardware that is not separation-relevant. For example, an FPGA doing cryptography can be under full control of a single partition.

#### 3.1.5 Security audit

Security audit, if it exists, is part of the MILS platform. Security audit is the trustworthy gathering of audit records. The audit records can be generated by the MILS core components or applications hosted by partitions.

A security audit component processes incoming data by adding trustworthy security related information such as time stamps and source of audit record. It can be local and managed by the audit component but also exported to an external media, this aspect being use-case implementation dependent.

December 2014 Page 14 of 63

#### 3.1.6 Middleware

Figure 4: MILS architecture template with middleware: components in dashed lines are optional.

The term middleware is generally not well defined and its meaning always depends on the context.

We define middleware as a set of services that are used by several partitions. Middleware does not contribute to the separation enforced by the MILS platform and is itself under control of the MILS platform, thus it is a unit (a partition) under control of the separation kernel. The system integrator of a MILS platform for a MILS system can decide to have middleware or not. Middleware can be a partition providing some functionality for several other partitions or be a part of a partition (e.g. libraries, runtime environments guest operating systems). For instance, the habitat of middleware is also restricted to be *within* a partition in [Win13, p. 3, Figure 2].

By introducing the concept of the middleware, we acknowledge that it can be useful to express that some partitions can be part of a bigger function (see Figure 4), and thus, need common infrastructure, which is not related to the MILS core or the MILS platform. In the generic MILS architecture template, we agreed to not use the term middleware to avoid any misunderstanding because it depends on the use-case where a MILS system is employed.

December 2014 Page 15 of 63

#### 3.2 MILS terminology

#### 3.2.1 Component

A component is a term to describe the decomposition of a (in general, any) system into meaningful self-contained parts. For example, a (yet to be defined) MILS system consists of components. In general, components may be implemented by (1) hardware, (2) software, or (3) a combination of hardware and software [CBB+03, DO-297]. A component provides a given functionality that can be configured according to a given use-case.

#### 3.2.2 Resource

A *resource* is anything (processor such as a CPU or a processing core, memory, software, data, network, etc.) internally used or exported by a component. A resource may be physical (a hardware device) or logical (a piece of information). A resource may be shared by multiple components or be dedicated to a specific component.

Exported resources are those resources to which an explicit reference is possible via a component interface, e.g., the programming or configuration interface. *Internal resources* are those resources used exclusively by the component, and which have no explicit reference via a component interface.

For example, internal resources of an operating system usually comprise physical memory space, I/O memory space, the set of processors the applications can run on, allocated processor time for each processor (at least, when the operating system is a real-time operating system), and interrupts. A resource commonly exported by an operating system is a "file". The operating system enforces an access control policy on the file. Internally, it uses memory to export the file. Another exported resource exported by an operating system is time slices, and the operating system enforces a scheduling policy (a resource management policy). Internally, the operating system uses CPU time that itself has access to.

#### 3.2.3 Communication object

A *communication object* is an exported resource provided by a component. It can be shared between components. Communication objects are used by components to communicate between them.

#### 3.2.4 Security policy

A *security policy* is a set of rules to be enforced by a component. Examples of security policies are:

- Resource allocation policy (Section 3.2.5)

- Access control policy (Section 3.2.6)

- Information flow policy (Section 3.2.7)

In our context, all three policies describe rules for granting or denying some "treatment" of exported resources, with "treatment" of a resource standing for to be able to eventually "read", "write", or "execute" the exported resource. The distinction

December 2014 Page 16 of 63

between the resource allocation policy and the access control policy is which interface the rules for access are applied on.

The term information flow policy has more than one usage, the most simple one is to use it as an umbrella term for "access control policy" and "resource allocation policy" combined. For most components, in the scope of this document, we adopt this simple interpretation, making these three security policies closely related. We decided not to merge the three policies in order to allow a precise characterization of components where needed later. Moreover, a more "complicated" usage of the term "information flow policy" will be encountered when the separation kernel is described (Section 3.2.13).

An operation might be governed by several policies: we consider both operations of "opening a file" and "reading/writing" to be involving access control to the file, however, the operation, depending on the implementation, could also be governed by a "resource allocation policy" such as the exclusive ownership of memory for the file descriptor to the component opening it. Similarly, the virtualization of a network component could comprise "access control" to Single Root I/O virtual functions and "resource allocation" if some of the virtual functions, after proper reinitialization, are assigned to different components during different periods of a time cycle (say 20 milliseconds each 100 milliseconds).

Note: We have observed that making the distinction between resource allocation policy and access control policy mixes concerns of interface (functional requirements) into policy requirements. However, the interface available to an attacker defines the possible malicious operations of the attacker. Thus, making the distinction allows to differentiate attacks based on resource depletion (attacking the resource allocation policy defined below) and attacks against confidentiality/integrity of the resources (attacks against the access control policy defined below).

A security policy can be dependent on system state, yet be bounded. For example, writing to a file may depend on that, statically, access to the file is allowed, and that, dynamically, a file descriptor is available after "opening" the file. Sometimes, in a usage that, after discussion, we do *not* follow in this document, the term "resource allocation" is used for initial establishment of a dynamic state, e.g. "opening a file" would be considered "resource allocation", whereas "reading/writing" the file would be governed by access control. For this document, as outlined above, we consider both operations of "opening a file" and "reading/writing" to be involving access control to the file.

When describing the protection of assets in the system, one can assume that every action that is eventually possible by configuration will be used by an attacker, even if some initialization of the state is needed. Thus, the static configuration describes a bound for the behaviour that is dynamically possible. Section 4.3 further discusses system configuration.

#### 3.2.5 Resource allocation policy

A component's resource allocation policy acts on the component's interface used to manage exported resources. This interface is characterized by that a request for a resource is made without knowing in advance how the resource is "named" or

December 2014 Page 17 of 63

"addressed". The request is made for a quantity of the resource, and then the component decides whether to grant or deny the request to export that resource in the desired quantity. The resource allocation policy defines which of the component's resources are kept internal to the component and which are exported to which other components. When a resource is exported to more than one other component, the resource is *shared*. A resource allocation policy can be in the "space" domain, when resources can be used simultaneously but are kept in different spatial (e.g. memory) locations or in the "time" domain, where resources are used sequentially, but kept in different time slices. An example for resource allocation in the "time" domain is the allocation of a CPU to a component for a limited period of time.

#### 3.2.6 Access control policy

A component's access control policy acts on the component's interface used to manage exported resources. In this respect it is identical to the aforementioned resource allocation policy (Section 3.2.5). However, the interface is characterized by that a request to the resource includes an explicit reference to the resource (e.g. the resource's name or a numerical identifier). Identically to the aforementioned resource allocation policy (Section 3.2.5), the access control policy defines which of the component's resources are kept internal to the component and which are exported to which other components. When a resource is exported to more than one other component, the resource is *shared*. The access control policy is in the "space" domain.

Note: as observed in Section 3.2.4, the resource allocation policy (Section 3.2.5) and the access control policy (this section) differ in the interface offered on the exported resources and they differ in the threats (exhaustion versus violation of integrity/confidentiality). For resource sharing, the threats a shared resource is exposed to are different: a resource shared under a resource allocation policy, e.g. a memory allocator that can be used by different components, can be exhausted ("denial of service"), but a resource shared by an access control policy, e.g. a piece of memory at a fixed address that is marked as accessible to several components, cannot.

#### 3.2.7 Information flow policy

The term *information flow policy* has more than one usage,

- (1) the most simple one is to use it as an umbrella term for "access control policy" and "resource allocation policy" combined or

- (2) to express policies where pieces of information (messages) are written to one or several communication objects(s) by a *sender* and subsequently these messages are read from the communication object(s) by a *receiver*. Such policies may include rules based

- (2a) on the sender/receiver of the messages and/or

- (2b) on the *content* of these messages.

Note: for most components, interpretation (1) is used. (2a) will be used in the context of a separation kernel (Section 3.2.13). The enforcement of (2b) is a typical task of

December 2014 Page 18 of 63

security gateway (discussed as an example in Section 3.3). An information flow policy in the sense of (2a) is either explicit, based on identities of components between which information flow is allowed, or implicit, as unambiguously defined by the resource allocation policy and access control policy.

#### 3.2.8 Configuration

The *configuration* of a component contains the component's identity, and it defines any security policy (access control policy, resource allocation policy, information flow policy) enforced by the component. An information flow policy configuration also may be implicitly configured by resource allocation policy configuration and access control policy configuration.

#### 3.2.9 Application

An application is one or more executable(s).

#### 3.2.10 Domain

A *domain* (or "security domain") is a unit of separation created and maintained by any MILS component, for example by an application (Section 3.2.9), a function (Section 3.2.12), or the MILS core (Section 3.2.14), which is enforcing a security policy on exported resources.

In particular, a domain is a "space" domain, if exported resources can be used simultaneously but are kept in different spatial (e.g. memory) locations. A domain is a "time" domain, if exported resources are used sequentially, but kept in different time slices.

#### 3.2.11 Partition

A *partition* is a component that serves to encapsulate application(s) and/or data. Thus, the content of a partition is application(s) and possibly other data. A partition is a unit of separation with respect to

- resource allocation in the space and time domains,

- an access control policy and an information flow policy in the space domain.

In a MILS system, partitions are created and maintained by the MILS core (see definitions below) based on security policies defined for a given use-case.

Note: this bottom-up definition of a partition has a different emphasis than the previous top-down characterization given in Section 3.1.4, but does not contradict it.

A partition is a domain, but a domain is not necessarily a partition.

#### **3.2.12 Function**

A *function* is a logical group of partitions for achieving common objectives. The implied partitions may be connected using information flows.

December 2014 Page 19 of 63

#### 3.2.13 Separation kernel

A separation kernel is a component that enforces a resource allocation policy and an access control policy on its exported resources (partition, resources allocated to a partition, communication objects). Communication objects allow for controlled information flow between partitions. A separation kernel may have an explicit or an implicit information flow policy on its partitions (see definition of information flow policy for details).

The separation kernel uses separation-supporting hardware to provide the separation between partitions in a MILS core.

#### Examples:

- A resource allocation policy might assign a certain amount of time, for example 20 milliseconds periodically every 100 milliseconds, of the resource CPU access to a certain partition, for example partition number 5.

- An access control policy might assign communication object C as writable to partition A and readable to partition B, defining an implicit information flow policy from A to B.

- An explicit information flow policy for a separation kernel could consist of the specification that only partition P via whatever interface may send information to partition Q.

#### 3.2.14 MILS core

By MILS core we refer to the minimal set of components needed for separation of partitions on a MILS platform. The only goal of *the MILS* core is to provide separated partitions with controlled information flow between them. Thus, the MILS core provides the primary security functionality of a MILS system. The MILS core (Figure 2) consists of components that implement and enforce the separation both in space and time.

#### 3.2.15 MILS platform

A *MILS platform* consists of the MILS core and optional software and/or hardware components that provide secondary security functionalities and do not contribute to the enforcing of separation.

#### 3.2.16 MILS system

A MILS system is a concrete deployment of a MILS platform with a defined set of partitions.

#### 3.2.17 MLS system

An *MLS system* is a system with different security requirements for different components. It can be implemented by a MILS system.

December 2014 Page 20 of 63

#### 3.2.18 Terminology rationale

The term *component* is a standard term for the description of software architectures (see also Section 2.4). On what can be a *component* we note that some presentations of MILS systems such as [UV05] come with a fixed number of layers. Others argue that, in principle, components themselves can contain MILS systems, allowing recursive compositions [Del12a, p. 56].

Resource: In software interface documentation, when specifying a component, we can describe what resources the component provides and what resources the component uses [CBB+03, p. 229]. In [SKPP, p. 21] resources that are provided by the component are called "external resources" whereas resources that are required by the component are called "internal resources". From a resource usage perspective, resources can either be hardware or resources provided by other components as in [Tan07, p. 432] where "a resource can be a hardware device (e.g. tape drive) or a piece of information (e.g. a locked record in a database)" or "Any element of a data processing system needed to perform required operations; for example: storage devices, input/output units, one or more processing units, data files, and programs." [ANS01]. The use of "resource" for describing hardware is also established in virtualization [PG74]. We have not found a stand-alone definition of the term "resource" in the MILS literature, but for separation kernels the hardware notion it appears close to [AFHOT06, p. 3] where the term is not explicitly defined. In the context of a description of a separation kernel, the term "shared resources" is expanded to "microprocessors, system registers etc." whereas the "piece of information" aspect appears to be addressed in [Rus08a, p. 10].

In [Rus08a], our resource allocation policy, access control policy, and information flow policy are equated to a "resource sharing" + (information flow) "policy". Also [SKPP] does not have any notion of an access control policy. We prefer to keep the three terms, because it simplifies mapping to [CC12], where the resource allocation policy can be mapped to the functional requirement class FRU\_RSA, the access control policy can be mapped to FDP\_ACF, and the information flow policy can be mapped to FDP\_IFF. That resource sharing implies information flows and that conversely resource sharing analysis supports information flow analysis is widely accepted [Kem83, AFOB+12]. Resource allocation policies versus access control list-based policies, e.g. the need to maintain resource exhaustion quantifiers to enforce resource allocation quotas, are discussed in [Ste91, p. 228].

Our definition of *application* is based on [ANS01]. It avoids any notion of user, as mentioning the term "user" at an early stage of the introduction could create the misunderstanding that users are limited to human beings using the system interactively.

The use of the term *domain* for environments where a security policy is imposed by a component can be found, for example, in [Lam71]. The same paper also shows (p. 428) examples for hardware-imposed domains (supervisor and software states) and software (user environments in an operating system).

Our definition of *partition* is close to [AFHOT06, p. 2] where a partition is defined as "a collection of data objects, code and system resources". [SKPP, p. 20] points out

December 2014 Page 21 of 63

that the term is motivated from its use in mathematics, where a partition of a set A is used to describe the split of a set into disjoint subsets, so that each element of A belongs to exactly one of the subsets.

Our definition of *function* (logical group of partitions for achieving common objectives) is what in [DO-297] is called an application.

*MILS platform* + *partitions content* = *MILS system*: this is emulated after IMA, where an IMA platform + partitions give an IMA system.

*MLS system:* We identify a MLS system with a system having different security requirements for different components. In safety, the term "mixed criticality" is often used for this. As discussed in Section 2.2, historically, there exists also a more restrictive usage, where a MLS system has a transitive security policy [BDR+08]. In line with many others (e.g. [DCS+04, LRP+11]), we do *not* adopt that more strict definition.

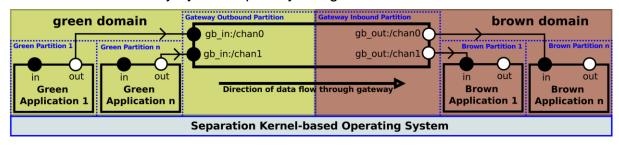

#### 3.3 Example of a MILS system

In this section the terminology of Section 3.2 is applied to a concrete MILS system described in [MPT+12]. The paper explains a gateway architecture implemented using the MILS principles for the purpose of controlling the content of the information flow between the hosted applications. Those applications process data of different security classification logically grouped into a green domain and a brown domain. As foundation, the gateway uses a separation kernel, which provides the functionality of partitioning and controlled non-bypassable information flow. Thus, the separation kernel applies a Resource Allocation Policy and maintains an Access Control Policy and a basic Information Flow Policy, defining the partitions that are allowed to communicate among each other. However, this Information Flow Policy of the separation kernel is not able to ensure additional constraints on content of the data that is transferred using the communication objects. The gateway enhances this Information Flow Policy by this capability using the available foundations.

Figure 5: Gateway architecture of a MILS system [MPT+12, Figure 3].

- Applying a black-box view from the outside onto the system in Figure 5, the system appears as a MLS system, since it processes data belonging to the green domain and data belonging to the brown domain concurrently.

- Having a closer look into the architecture of the system, the system is a MILS system, since it uses a MILS platform (the Separation Kernel-based Operating System) and partitions identified by the blue dotted lines in Figure 5.

- The MILS platform comprises the Separation Kernel-based Operating System (the MILS core) plus the Auditing Module mentioned in [MPT+12, Section II.D].

December 2014 Page 22 of 63

- The *MILS core* is the Separation Kernel-based Operation System [MPT+12, Section II.D] plus some unspecified hardware (that is not further described in [MPT+12]) but used and managed by this separation kernel.

- As Separation Kernel the example uses PikeOS [MPT+12, Section II.D]. This separation kernel enforces the Resource Allocation Policy and Access Control Policy to form partitions (the blue dotted boxes) based on the available resources, such as memory, CPU cores and the program binaries. The separation kernel exports some of those resources for building communication objects. By controlling the accesses of the partitions to those exported resources the separation kernel creates and applies a basic Information Flow Policy. Examples for exported resources are: ARINC 653 ports or file providers [MPT+12, Section IV.C].

- Partitions are provided by the separation kernel. The gateway relies on this crucial element for implementing its function.

- Within the partitions the example executes several Applications, which is the

content of the six blue dotted boxes in Figure 5. The paper specifies

applications running within the "Gateway Outbound Partition" and within the

"Gateway Inbound Partition". Other applications are the Brown Applications

and Green Applications.

- As components the modules of [MPT+12, Section IV.II], such as the modules with specific functionality for filtering packets (named "Viewer Module"), reading/writing filtered packets across partitions ("Border-crossing Module") or making decisions on packet routing ("Routing Module") can be identified. The paper does not explicitly identify hardware; however it is assumed that the system contains at least a CPU, which again is a (hardware) component.

- The purpose of the gateway is to enhance the basic Information Flow Policy of the Separation Kernel by the ability of controlling the content of the information flow (unidirectionally) [MPT+12, Section IV.I] and [MPT+12, Section V]. For achieving this logical *function*, the gateway uses the collaboration of two partitions: the Gateway Outbound Partition and the Gateway Inbound Partition. Other functions are given by the applications located inside the two security domains, which "can comprise one or more partitions" [MPT+12, Section IV]. Functions are depicted as a black solid boxes in Figure 5.

- The system contains *configurations* of different applications:

- The configuration of the gateway for defining the enhanced Information Flow Policy.

- The configuration of the separation kernel for defining the Resource Allocation Policy and the Access Control Policy for the gateway components [MPT+12, Section IV.II]. [MPT+12, Section IV.III] forces the system integration to provide "enough buffer space" for the exported communication objects. [MPT+12, Section IV.IV] discusses the scheduling configuration of the system. Non-bypassability of the gateway's enhanced Information Flow Policy is ensured by the separation kernel.

December 2014 Page 23 of 63

## **Chapter 4 MILS main components**

The following characterization of components does *not* include all MILS components, but rather discusses the security properties of MILS components that are common to MILS platforms and occur frequently. We begin with software components (Section 4.1), followed by hardware components (Section 4.2) and discuss the configuration of MILS systems (Section 4.3).

#### 4.1 Software components

#### 4.1.1 Separation kernel

A concise characterization of a "separation kernel" already has been given in Section 3.2.13. In this section, we look at the "separation kernel" as a MILS software component.

#### **4.1.1.1 Services**

#### 4.1.1.1.1 Pictorial view

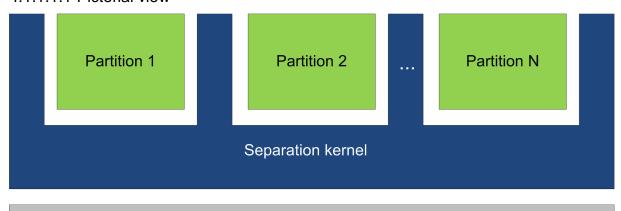

Figure 6: Generic picture of a separation kernel with several partitions.

Hardware

The pictorial view is the most commonly found way to describe the services of a separation kernel. Figure 6 shows that each partition is under control of the separation kernel, in the sense that the separation kernel enforces the system configuration upon all their communication and resource requests in a non-bypassable way, while it is not inspecting or protecting what happens within the partition itself. For example, if a partition is authorized to communicate over a network and to use the HTTP protocol, the SK will not protect the application against infection by a virus introduced into the HTTP payload.

December 2014 Page 24 of 63

#### 4.1.1.1.2 Classical approach

In some of the early work such as [BBH+05, UV05, AFHOT06] a strong emphasis on the implementation of information flow and its absence has been taken.

- "The only tasks assigned to a MILS separation kernel are the partitioning of processes and failure containment. Consequently, we can represent the safety and security requirements for a separation kernel by four simple foundational policies:

- **Data Isolation**: Information in a partition is accessible only by code running in that partition. Private data remains private.

- Control of Information Flow: Information flow among partitions is from an authenticated source to authenticated recipients. The source of information is authenticated to the recipient. Information goes only where intended.

- **Resource Sanitization**: Usage of the microprocessor and other hardware, such as networking hardware, cannot be used as covert channels to leak information.

- **Fault Isolation**: A failure in one partition is prohibited from cascading to any other partition. Failure detection, containment, and recovery are performed locally" [UV05].

Similar formulations are found in an early draft of an SKPP predecessor (defining "data isolation", "control of information flow", "resource sanitization") [WOM02].

#### 4.1.1.1.3 Policy-based description

For convenience, we repeat our definition from Section 3.2.13.

"A separation kernel is a component that enforces a resource allocation policy and an access control policy on its exported resources (partition, resources allocated to a partition, communication objects). Communication objects allow for controlled information flow between partitions. A separation kernel may have an explicit or an implicit information flow policy on its partitions (see definition of information flow policy for details).

The separation kernel uses separation-supporting hardware to provide the separation between partitions in a MILS core."

We think this description with an emphasis on policies fits better in a systematic exposition. A description based on policies has also been adopted in the "MILS constitution" [Rus08a], another attempt to systematically explain MILS.

This characterization is isomorphic to the characterization of Section 4.1.1.1.2: "resource sanitization" and "damage limitation policies" are implied by the requirement of complete information flow control. "Data isolation" is the default of the access control policy, resource allocation policy and information flow policy on internal resources, whereas "control of information flow" addresses the access control policy, resource allocation policy and information flow policy on external resources.

December 2014 Page 25 of 63

## 4.1.1.4 Description of functionality grouped according to where separation is made (space/time)

In the following paragraphs, we present the approach taken in [TBF13] then we comment it versus previous sections (i.e., classical approach and policy-based description).

**Separation in space**: Applications can be hosted in different partitions. Partitions get assigned memory resources (i.e. space). In this way, the separation kernel enforces its configuration: that is, access control on partition content, per-partition provision of physical memory space and I/O memory space. By confining applications into partitions, the separation kernel enforces that these applications can affect neither applications in other partitions nor the separation kernel itself.

**Separation in time**: Applications can be hosted in different partitions. Partitions get assigned CPU time (i.e. time windows). In this way, the separation kernel enforces its configuration: that is the allocation of a predefined amount of the CPUs' time to partitions. Several partitions can share the same time window. On a partition switch CPUs will be reused. The separation kernel enforces that no residual information is in CPU registers or memory caches according to the configuration. The separation kernel assigns a priority to every subject to allow priority based scheduling within one time window.

**Provision and management of communication objects:** Applications hosted in different partitions can get assigned a set of communication objects under control of the separation kernel. A communication object is an object exposed to one or multiple partitions with access rights as defined in the configuration data, thus allowing communication between partitions.

**Separation kernel self-protection and accuracy of security functionality:** Separation kernel self-protection and accuracy of functionality supports reaching and keeping a safe and secure state of the MILS system. The separation kernel statically assigns automatic invocations of error handling functions to recover from or respond to error conditions.

Again, this characterization is isomorphic to the characterization of Section 4.1.1.1.2 and Section 4.1.1.1.3. Like the one of Section 4.1.1.1.2, it is optimized to be standalone and concrete. It splits up the data isolation of Section 4.1.1.1.2 of into "separation in time" and "separation in space". The "resource sanitization" of Section 4.1.1.1.2 is subsumed under "separation in time". "Control of information flow" is represented by "provision and management of communication objects". "Fault isolation" is subsumed under "separation in space" and "self-protection".

Also in the SKPP, while claimed as security functional requirements, "fault containment" and "resource sanitization" are *not* listed explicitly in the introductory high-level characterization of "core functional requirements" [SKPP, p. 25].

#### 4.1.1.1.5 Virtualization services on top of separation kernels

Virtualization is *not* a necessary part of separation kernels. However, because many separation kernel deployments provide support for virtualization services, the concept

December 2014 Page 26 of 63

is described here. We discuss these concepts in form of tables (Table 2 and Table 3), juxtaposing a generic description of virtualization and the analogous or differing complement in a separation kernel.

A *virtual machine (VM)* consists of software that imitates a physical hardware machine. The virtual machine will for example give the illusion of a physical CPU and physical memory to an operating system that is running in it. An operating system running in a virtualization environment is called *"guest"*. In the MILS context, a virtualized operating system is a special case of an application (the term "application" was defined in Section 3.2.9).

A virtual machine monitor (VMM), also called a "host" (for type 2 VMMs) or "hypervisor" (for type 1 VMMs, see Table 2 for type 1 and 2 explanation), is the software managing virtual machines.

#### **Requirements:**

Table 2 lists virtualization requirements in general and their fulfilment or non-fulfilment by a MILS separation kernel.

| Virtualization Requirement in General                                                                                                                                                    | Virtualization Requirement Compliance in a MILS Separation Kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| An operating system running on a VMM is characterized by:  (1) the resource control property, that the VMM is in complete control of system resources, [PG74]                            | Concerning (1), the resource control property: In MILS systems, the resource control property is implemented by the separation kernel via its security policies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| An operating system running on a VMM is characterized by:  (2) the sufficiency property, that a VMM provides an environment for the operating system which is sufficient for running it. | Concerning (2), the sufficiency property: The sufficiency property means that the API provided by a MILS system to its applications does not have to provide the same API as in virtualization of a machine, e.g. for a MILS system it is sufficient to provide communication channels instead of, for example, a network interface, but it need not necessarily provide a full replica of another machine. In a VMM, the API is the full CPU instruction set. When under a VMM, a VM attempts to execute an instruction that only runs in supervisor mode of CPU, VMM intercepts this attempt and VMM tries to emulate the instruction as faithfully as possible. In a separation kernel, when an application in |

December 2014 Page 27 of 63

| Virtualization Requirement in General                                                                                                                                                                                                         | Virtualization Requirement Compliance in a MILS Separation Kernel                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                               | a partition executes an instruction that only runs in supervisor mode, the SK traps it, and usually its execution is rejected. Instead, the separation kernel offers explicit additional interfaces to allow partitions to do certain things (e.g. create new thread within a partition, use a new address space within a partition, access a shared resource etc.). The main difference would be that VMM tries to create virtual environment but SK does not. |

| An operating system running on a VMM is characterized by:  (3) the isolation property, that is applications running in different VMs do not interfere with each other                                                                         | Concerning (3), the isolation property: this is provided by the fact that the separation kernel enforces temporal and spatial separation properties on applications.                                                                                                                                                                                                                                                                                            |

| An operating systems running on a VMM is characterized by:  (4) the efficiency property that programs run on VMM with only minor decreases in speed [PG74]                                                                                    | Concerning (4), the efficiency property: While, in practice, the efficiency property is probably fulfilled by most MILS systems, the emphasis is less on good average application performance but rather on guaranteed real-time worst case execution time bounds.                                                                                                                                                                                              |

| (5) While virtualization has traditionally been focusing on the isolation of virtual machines hosted by the same hardware platform, controlled resource sharing, such as for example a common storage, can also be a desired feature [Kar05]. | Concerning (5) controlled resource sharing: it is well supported by communication objects.                                                                                                                                                                                                                                                                                                                                                                      |

Table 2: Virtualization requirements: in general and their compliance with MILS SK

(Note: instead of the sufficiency property and isolation property [PG74] gives the stronger equivalence property, that a VMM provides an environment for programs which is essentially identical with the original machine, except for timing effects. Our definition is broader to allow for paravirtualization, see below.)

#### **Implementation:**

December 2014 Page 28 of 63

Table 3 lists virtualization implementation characteristics in general and their applicability or non-applicability in a MILS separation kernel.

| Virtualization Implementation Characteristics (of an Operating System) in General                                                                                                                                                                                                                                                                                                                                 | Virtualization Implementation Characteristics (of a MILS application) in a MILS Separation Kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |